1 引言

数字电源是指以数字芯片为核心,实现数字控制和通信功能的电源产品。浪涌是一种突发性的瞬态电压或电流脉冲,本质上是一种微秒级别的剧烈脉冲。在航天、通信等行业中,当浪涌发生时,不仅要求数字电源可以承受瞬态电流尖峰的冲击,同时还要求数字电源能正常可靠地运行。

通常数字电源的交流输入端已设置浪涌防护模块,在直流输出端也有稳压限流等措施;但是浪涌产生时,电源内部乃至直流输出端仍然有可能出现瞬间的大电流脉冲。大电流脉冲有可能造成半导体元器件可靠性降低、损坏甚至电源故障;还可能会导致输出电压电流异常和电磁干扰,影响下一级设备的工作。因此,研究数字电源浪涌抑制方法有着重要的意义。

为提高数字电源浪涌抑制能力,国内外学者致力于浪涌抑制技术的研究,以期在浪涌产生时,保障电源可靠工作。文献[1]提出一种(Insulated gate bipolar transistor,IGBT)和继电器组合的快速开关电路,利用压敏电阻、安规电容等元器件抑制雷击浪涌影响;但在该电路中,当N线受到雷击浪涌影响时,并联在IGBT两端的二极管易先于IGBT体二极管导通而损坏。文献[2]对光伏并网发电系统中一种直流电涌保护器进行了特性分析,不足在于单个直流电涌保护器无法完全滤除浪涌干扰,需要多级浪涌保护器的联动配合,这势必会增加系统的体积与成本。文献[3]提出了一种电源防护系统,该系统利用双重隔离以提高电源线路的防雷水平,该系统对雷击电磁脉冲有很好的防护效果,但是该设计中的隔离变压器降低了系统效率,增加了体积与成本。文献[4]使用瞬态保护与频域滤波结合的方法设计了一种针对电源线的纳秒级电磁脉冲干扰综合防护模块,该模块可在较短时间内泄放掉大部分的浪涌能量,但因模块元器件自身寄生效应的存在,该模块无法克服浪涌对模块后级电路的影响。文献[5]对直流电源输入端的浪涌抑制技术进行了研究,对不同电压等级的浪涌提出了不同的抑制电路,但是浪涌强度通常会随着环境变化而动态变化,单一电路对浪涌的变化缺乏适用性。

上述研究多是通过在系统前端加装防浪涌模块的方法进行浪涌抑制,但是防浪涌模块自身会产生一定的寄生效应。同时,防浪涌模块的设计需要综合考虑工作电压、通流能力、响应速度等多项因素,且受限于器件自身特性,仅靠防浪涌模块进行浪涌抑制效果并不理想。

针对前端浪涌防护模块抑制浪涌能力不足的问题,本文对浪涌特性及浪涌在电源内部传递路径进行深入分析,对数字电源前端的浪涌防护模块进行优化;同时,应用印刷电路板(Printed circuit board,PCB)布局优化、电路优化及磁屏蔽等方法对浪涌防护模块后端的残压进行滤除。1.2 kW试验样机试验结果表明,所优化的浪涌防护模块及所提浪涌抑制方法可以有效地抑制浪涌对电源正常工作的影响。

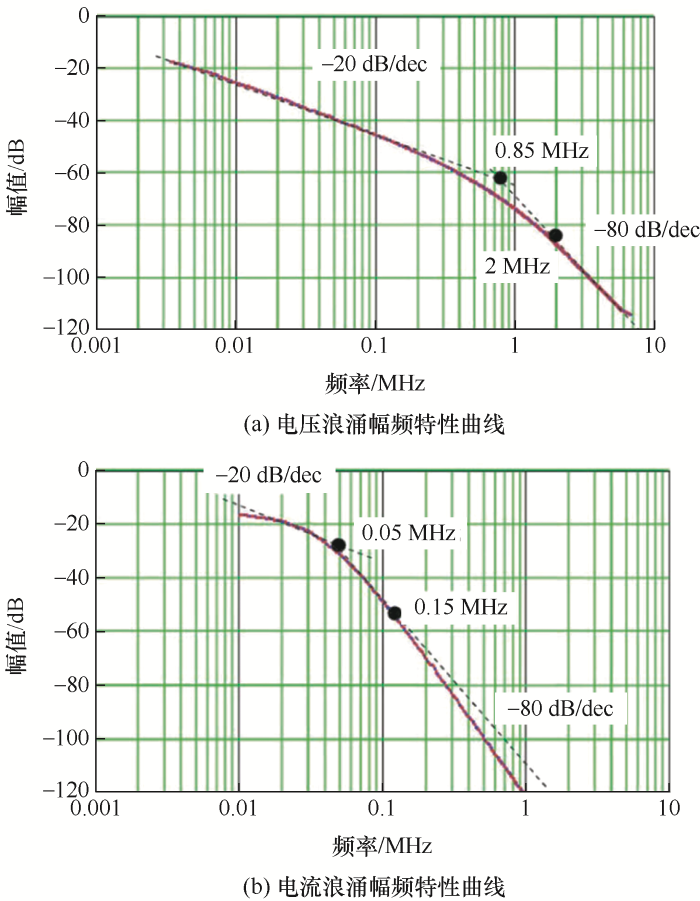

2 浪涌特性

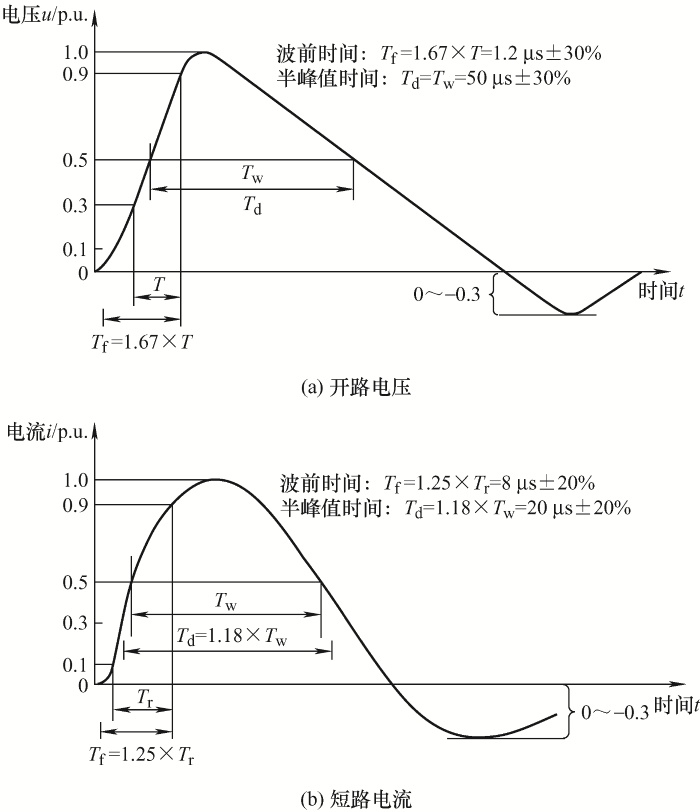

表1 浪涌波形特征参数

| 参数 | 定义 |

|---|---|

| Tw | 波形上升至50%峰值后下降其峰值50%的时间间隔 |

| T | 电压波形由30%峰值上升至90%峰值所对应的时间间隔 |

| Tr | 电流波形由10%峰值上升至90%峰值所对应的时间间隔 |

| Tf | “波前时间”,对于电压波形来说,Tf=1.67T,对于电流波形来说,Tf=1.25Tr |

| Td | “半峰值时间”,对于电压波形来说,Td=Tw,对于电流波形来说,Td=1.18Tw |

图1

图2

3 浪涌传递路径

3.1 浪涌在数字电源中传递路径

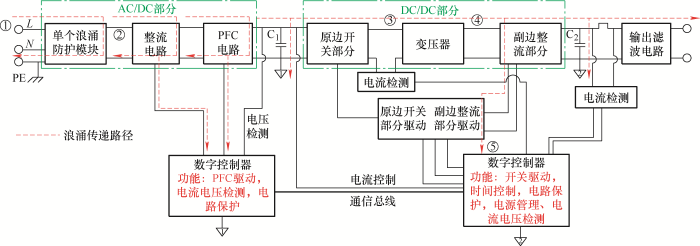

数字电源结构框图如图3所示,由前端AC/DC部分和后级DC/DC部分组成。

图3

前端交流电与直流电(Alternating current/ direct current,AC/DC)部分包括浪涌防护模块、整流电路及功率因数校正(Power factor correction,PFC)电路,后级DC/DC部分包括原边开关部分及副边整流部分,两部分均由数字控制器进行控制。输入交流电经浪涌防护模块和整流电路作用后变为直流,后经PFC功率因数校正后由大容量电容C1进行稳压。后级DC/DC变换器将C1上的稳定电压进行电压变换,变换后的电压经输出滤波后供下一级设备直接使用[11]。

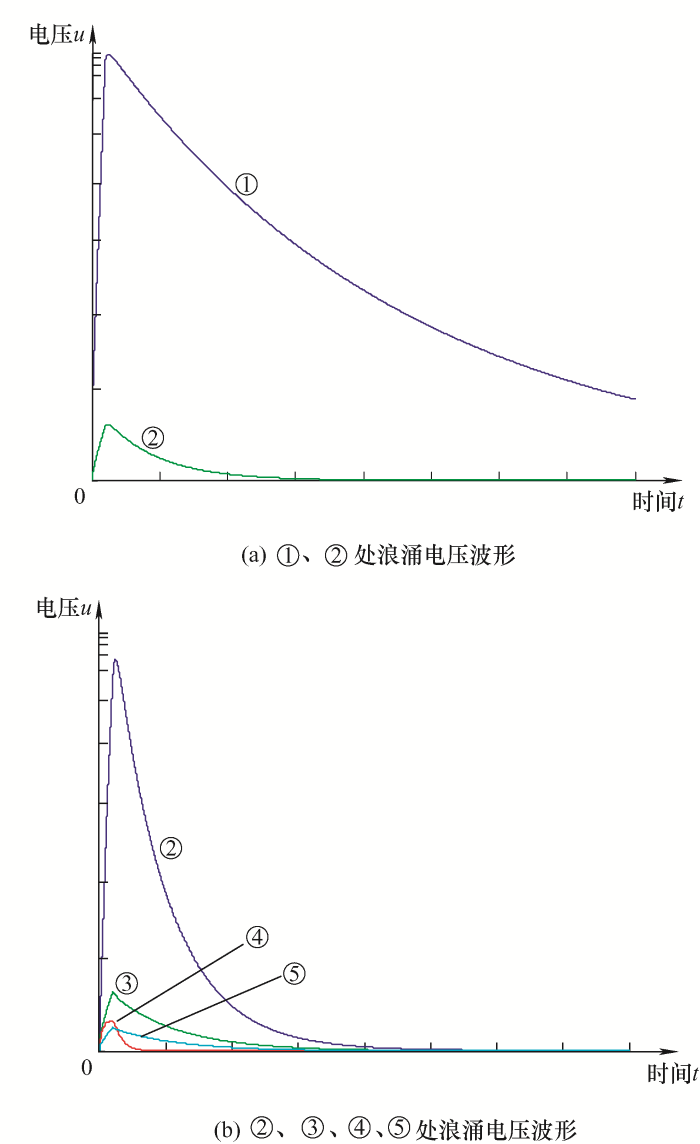

数字电源的浪涌传递如图3中虚线所示,图3中虚线粗细代表浪涌能量的强弱,由图3可知,浪涌能量在单个浪涌防护模块部分最强,经单个浪涌防护模块浪涌抑制作用后,浪涌能量变弱。根据IEC 61000-4-5,当电路施加波前时间1.2 μs及半峰值时间50 μs的开路浪涌电压时,图3中①~⑤处电压波形如图4所示,图4中,线①表示图3中①处电压,是电源输入处浪涌电压波形,线②表示图3中②处电压,是经浪涌抑制器作用后的电压波形,由线②可知,经浪涌抑制器作用后,浪涌电压依然具备标准所描述的波形特征,但是幅度大为降低。线③表示图3中③处电压,为DC/DC变换器原边处浪涌波形,经电容C1作用后,浪涌电压幅值进一步降低,但是依然存在,线④表示图3中④处电压,为变压器副边浪涌电压波形,线⑤表示图3中⑤处电压,为DC/DC部分芯片供电端浪涌电压波形。

图4

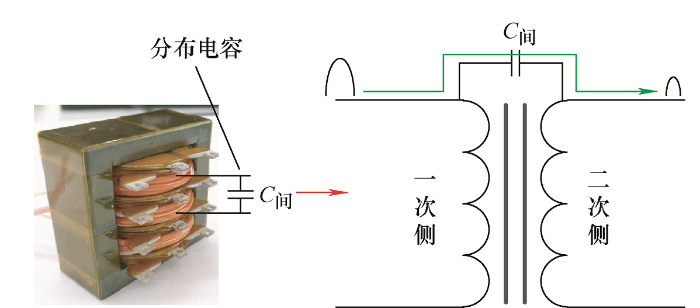

3.2 浪涌对变压器二次侧的影响

图5

4 浪涌抑制方法

现根据数字电源的输入输出能量传递顺序对数字电源的浪涌抑制方法进行研究。

4.1 AC/DC部分浪涌抑制方法

AC/DC部分包括浪涌防护模块、整流电路及PFC电路,分别进行浪涌抑制、交-直流变换及功率因数的提高。

4.1.1 浪涌防护模块优化

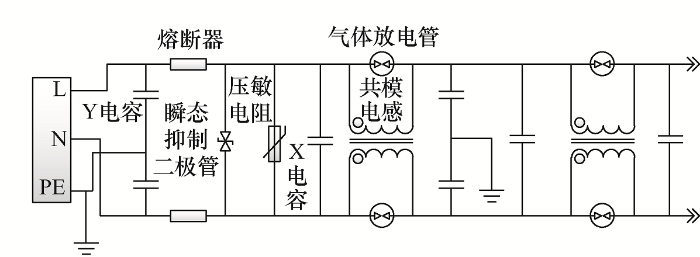

浪涌防护模块不仅要进行浪涌抑制,也要兼顾电磁兼容性能。浪涌防护模块主要由压敏电阻、瞬态抑制二极管、气体放电管、X电容、Y电容及共模电感等元件组成,浪涌防护模块电路如图6所示。

图6

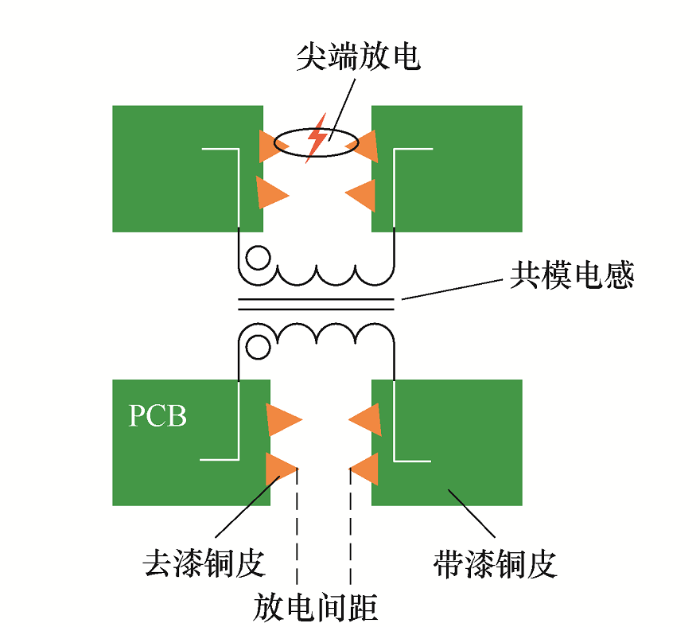

此外,可采用PCB板尖端放电的方式进行能量泄放,如图7所示。

图7

在共模电感两端放置放电齿,放电齿表面进行开窗不敷漆,使得共模电感两端产生的瞬态高压可以通过放电齿尖端进行放电,进而减少甚至避免通过其他路径放电,这种方法能够有效保护周围和后级器件。

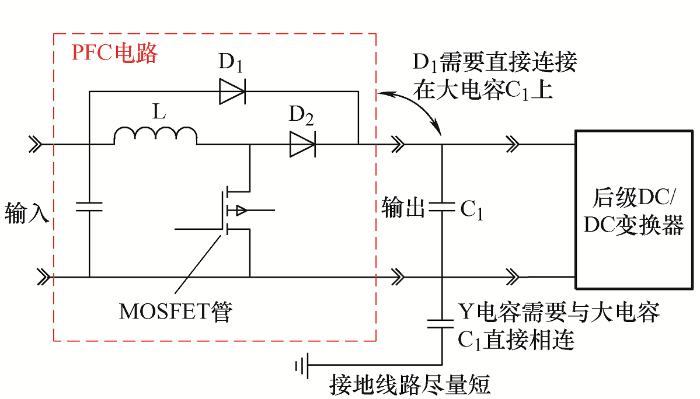

4.1.2 PFC部分的浪涌抑制方法

前端浪涌防护模块对瞬态浪涌进行一次性的抑制,对浪涌的低频分量进行消耗时,也可让高频分量进行衰减,同时它几乎不影响电源系统的正常工频运行状态,但是数字电源的耐压水平较低,前端浪涌防护模块不能完全满足电源的安全工作要求, 为提高设备的可靠性和安全性,则需要模块后的PCB布局优化、电路优化等手段对浪涌防护模块后端残压的传递路径进行控制,促使残压以最短的路径通过N线或PE线进行泄放。

数字电源电流和电压之间的相位差会造成交换功率的损失,此时便需要PFC电路提高电路的功率因数,功率因数值越高,电能利用率越高。

PFC电路浪涌抑制方法如图8所示,PFC电路由储能电感器L、MOSFET管、快恢复二极管D2组成等元件组成,为防止功率MOSFET因大电流的冲击损坏,增加旁路二极管D1,以降低功率MOSFET的最大峰值电流。根据浪涌标准IEC 61000-4-5,浪涌波前时间仅有1.2 μs,因此,旁路二极管的开启时间必须小于1.2 μs,同时,要优化PFC电路的PCB布局,以减少浪涌对后级DC/DC部分的影响,PCB布局具体优化要点如下:① D1需要直接连接在大电容C1上,且线路尽量短;② Y电容需要与大电容C1直接相连;③ Y电容接地线路尽量短。

图8

4.2 DC/DC部分浪涌抑制方法

DC/DC部分的主要作用是将AC/DC变换后的电压进行再次变换,以供输出使用,数字电源以数字芯片为控制核心,数字芯片因供电电压较低易受浪涌影响,故在DC/DC部分,数字电源主要以减少浪涌对数字芯片的影响为主要控制目标。

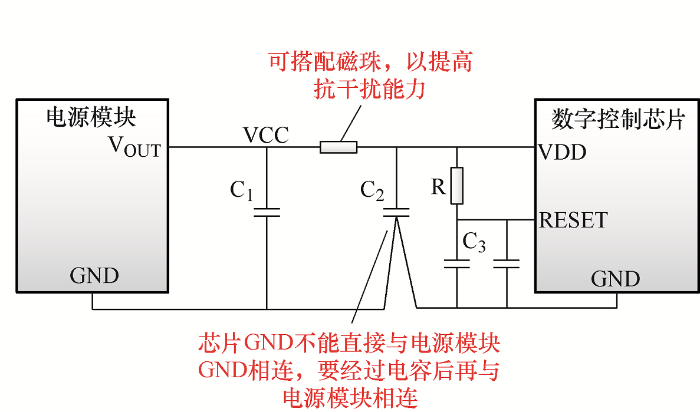

(1) 为抑制浪涌电流的冲击,数字控制芯片工作电压(Voltage drain drain,VDD)端及RESET端电路优化应如图9所示。电路供电电压(Voltage collector collector,VCC)端在连接至数字控制芯片RESET端时,应加入滤波电路,滤波电容C3应至少由两种容值组成,且滤波电容C3应紧贴RESET端放置。同时,可搭配磁珠以提高抗干扰能力。

图9

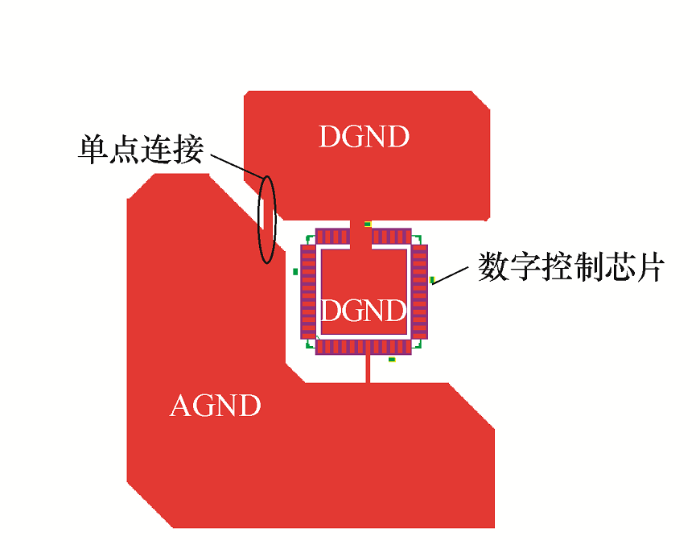

(2) 在优化电路的同时,也要通过优化PCB板布局滤除浪涌的干扰,数字控制芯片下方要保证完整的敷铜。数字控制芯片的模拟地线(Analogue GND,AGND)要和数字地线(Digital GND,DGND)单点连接,如图10所示。

图10

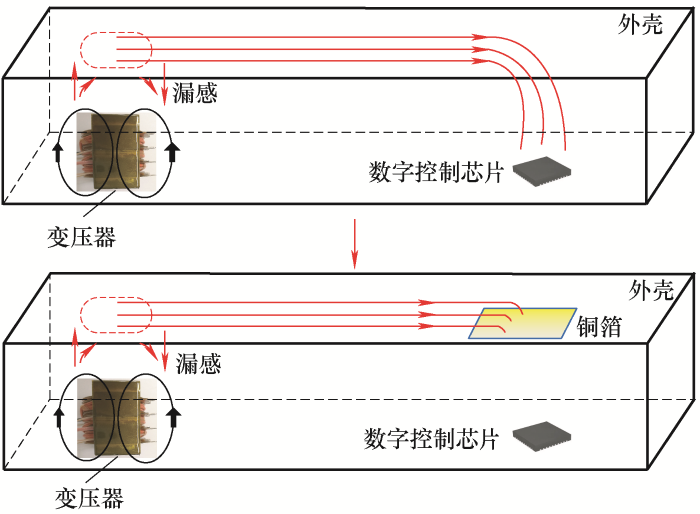

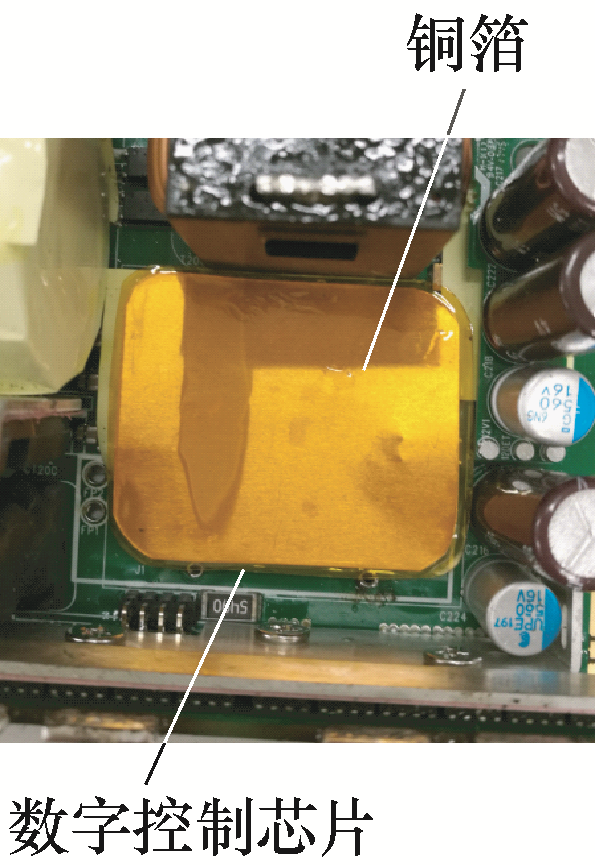

(3) 对于DC/DC部分来说,当浪涌发生时,变压器磁场也是一个重要的干扰源[17]。铁、铁硅系合金为导磁性材料,非常适合磁能的传导,若选用铁磁性材料作为电源外壳的话,变压器上因浪涌产生的磁干扰易通过外壳传导至变压器二次侧数字芯片处,影响数字控制芯片的正常运行。

图11

5 试验研究

表2 样机主要技术参数

| 参数 | 数值/型号 | 备注 |

|---|---|---|

| 输入电压/V | AC220 | |

| 主路输出电压/V | DC54 | |

| 辅路输出电压/V | DkC12 | |

| 开关频率/kHz | 240 | |

| 负载功率/kW | 1.2 | |

| PFC电路开关管 | IPW60R080P7 | INFINEON公司 |

| DC/DC部分原边开关管 | IPW60R037P7 | INFINEON公司 |

| DC/DC部分副边整流管及续流管 | FDMS86 350 | Fairchild公司 |

| AC/DC部分控制芯片 | UCD3 138 | TI公司 |

| DC/DC部分控制芯片 | UCD3 138 | TI公司 |

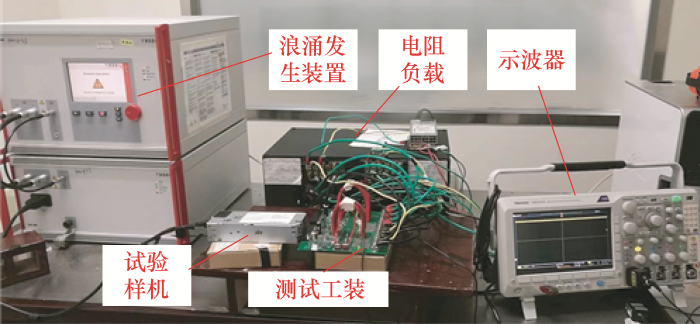

图12

表3 差模浪涌测试结果

| 测试 电压/kV | L与N相位差/(°) | |||

|---|---|---|---|---|

| 0 | 90 | 180 | 270 | |

| 1 | 工作正常 | 工作正常 | 工作正常 | 工作正常 |

| 1.5 | 工作正常 | 工作正常 | 工作正常 | 工作正常 |

| 2 | 工作正常 | 工作正常 | 工作正常 | 工作正常 |

表4 共模浪涌测试结果

| 测试电压/ kV | L与N相位差/(°) | 备注 | |||

|---|---|---|---|---|---|

| 0 | 90 | 180 | 270 | ||

| 1 | 工作正常 | 工作正常 | 工作正常 | 工作正常 | |

| 2 | 工作正常 | 工作正常 | 工作正常 | 工作正常 | |

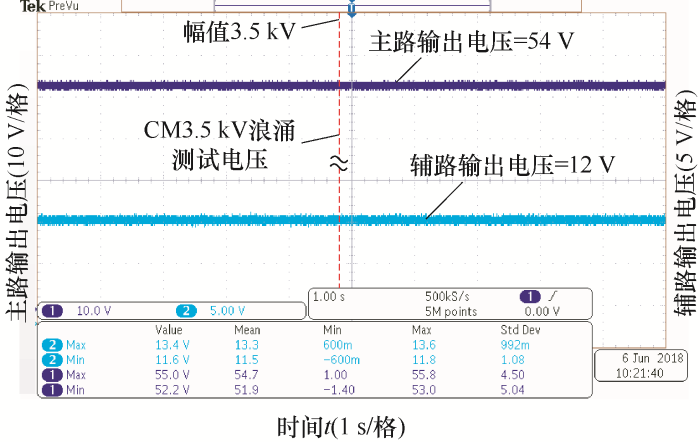

| 3 | 工作正常 | 工作正常 | 工作正常 | 工作正常 | |

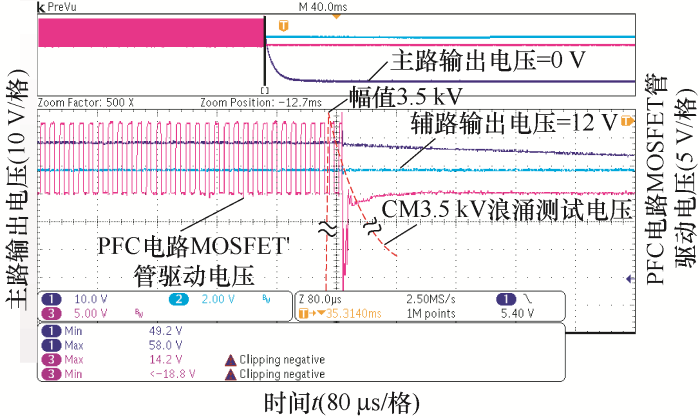

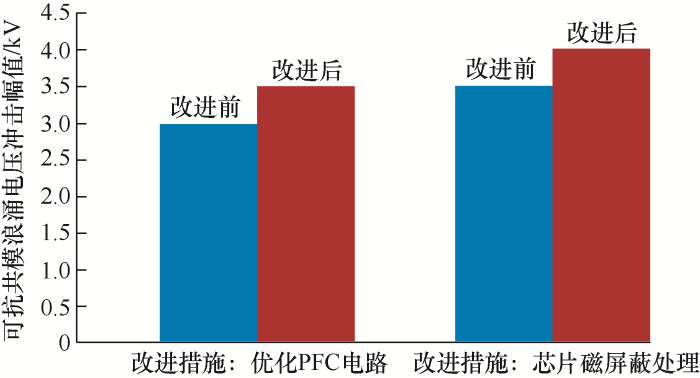

| 3.5 | 工作正常 | PFC电路MOSFET管损坏,主路电压无输出 | 工作正常 | 工作正常 | 优化PFC电路的PCB布局后通过该电压等级测试 |

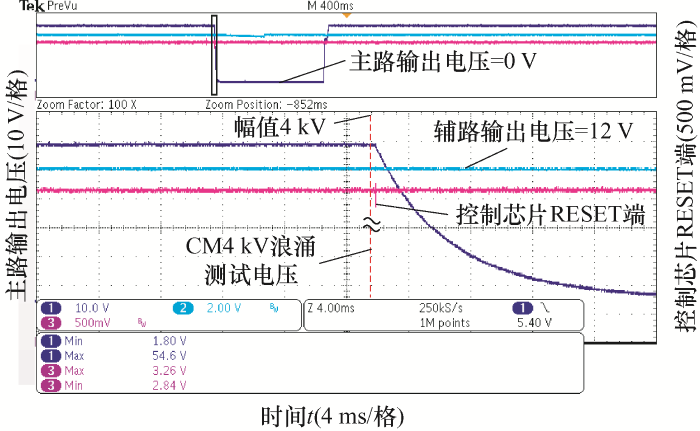

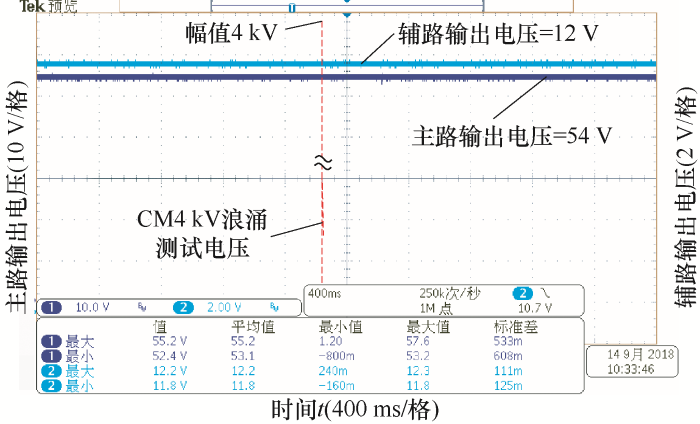

| 4 | 工作正常 | 主路电压输出重启,数字控制芯片重启 | 工作正常 | 工作正常 | 对DC/DC部分数字芯片进行磁屏蔽后通过该电压等级测试 |

图13

图14

图15

图16

图17

图18

6 结论

本文分析了浪涌产生的原因、浪涌的特性及在数字电源中的传递路径,研究了浪涌在不同观测点的波形及对变压器二次侧的影响,依次对AC/DC部分及DC/DC部分的浪涌抑制方法进行探究。

(1) 优化了浪涌防护模块,通过浪涌抑制元器件的串并联组合将浪涌能量逐级泄放,同时采用PCB板尖端放电的方式在共模电感两端对能量进行泄放。

(2) 在PFC电路部分,通过电路优化及PCB布局优化的方式提高浪涌抑制能力。

(3) 在DC/DC部分通过滤波电路设计、PCB布局优化及磁屏蔽等方法提高数字芯片的浪涌抑制能力。

本文所提方法原理简单,可靠性高。试验结果表明通过本文所提新方法,数字电源能获得良好的浪涌抑制能力,可抗4级浪涌试验,输出电压稳定无奇异点,无掉电或重启等异常情况发生。

参考文献

基于IGBT的快速开关电路抗雷击浪涌设计

[J].

Design of rapid switch circuit anti-lightning surge based on IGBT

[J].

单相交流电源隔离防护设备设计

[J].

Design of single-phase protecting device for isolation from alternating current supply

[J].

电源线纳秒级电磁脉冲骚扰防护模块设计

[J].

Design of protection module against disturbance induced by nanosecond electromagnetic pulse on powerline

[J].

直流电源引入端浪涌抑制技术研究

[J].

Research on surge suppression technology at the inlet of DC power supply

[J].

航天器开关上电脉冲抑制方法研究

[J].

Research on power-on pulse suppression method for spacecraft switch

[J].

DOI:10.13234/j.issn.2095-2805.2022.5.60

[本文引用: 1]

Switch power-on pulses are widely found in aerospace power distribution systems which use mechanical switches as power distribution controls. The pulse peak generation time is earlier than that of the conventional surge current, the pulse peak value is hundreds of times higher than that of the steady-state current, and the rising edge reaches an order of nanosecond, which is harmful to the power distribution system. Through the analysis of the switch power-on pulse generation mechanism, the difference between the switch power-on pulse and conventional surge current is compared, and the advantages and disadvantages of several switch power-on pulse suppression methods are analyzed. Finally, an optimal suppression scheme is given. Based on the principle of pre-charging, this scheme connects the small switch series resistance branch in parallel with the original power switch branch, and designs a driving sequence ingeniously. On the premise of not increasing the resources such as instructions and weight, the power-on pulse is controlled within an expected index, which solves the problem that the conventional surge circuit cannot suppress the switch power-on pulses.

Operation and analysis of non-isolated high-voltage-gain DC-DC boost converter with voltage multiplier in the DCM

[C]//

浪涌抑制技术研究

[J].

Study on the surge suppression

[J].

基本直流/直流变换器及直流分布式电源系统拓扑分析

[J].

Topology analysis of the basic DC to DC converter and DC distributed power system

[J].

雷达站电源综合防雷系统研究与设计

[J].

Study and design of comprehensive lightning protection system for power supply of radar station

[J].

基于差模共模保护模式下的交流电源端口浪涌防护对比分析

[J].

Comparison and analysis of surge protection for AC power port based on the protection mode of differential mode common mode

[J].

Two-capacitor transformer winding capacitance models for common-mode EMI noise analysis in isolated DC-DC converters

[J].DOI:10.1109/TPEL.2017.2650952 URL [本文引用: 1]

Impact of parasitic inductance on effectiveness of TVS diodes

[C]

瞬态抑制二极管(TVS)的试验分析与应用

[J].

Experimental analysis and application of transient voltage suppressor

[J].

Immunity requirements for secondary equipment with regard to switching operations of disconnectors in substations

[C]//

基于Ansoft的空心电抗器磁屏蔽研究

[J].

Magnetic shielding research of air-core reactor based on Ansoft

[J].

谐波激励下变压器铜屏蔽杂散损耗的计算和验证

[J].

Calculation and verification for stray loss of transformer copper shield under harmonic excitation

[J].

铜屏蔽层对高速永磁无刷直流电机转子涡流损耗和应力的影响分析

[J].

Influences of copper shield on eddy-current loss and stress for a rotor of high-speed PM BLDC motor

[J].